- 九游游戏中心打造最热门游戏,从运营入手,BAT等一线互联网公司的进阶之

- 穿越火线游戏下载(获取最新版本的游戏安装包)

- 实用韩语500句谐音(学习韩语必备的实用口语)

- 手机QQ2013安卓老版本下载指南(兼谈如何避免版本更新带来的问题)

- 在线登录qq不用下载(轻松实现qq在线登录的方法)

- 一点通驾校模拟考试,帮你轻松通过驾照考试

- 一嗨租车有哪些优惠活动?

- 听歌不再枯燥,百度在线听歌曲大全带你畅游音乐世界

- 百度云下载方法及注意事项

- 全国高清电视直播下载(观看高清电视直播的优秀途径)

- 诺基亚历史机型大全,了解诺基亚手机的发展历程

- 播放器软件大全推荐,哪个好用?

- CF手游单机版如何下载及安装?

- 如何获取免费的北斗卫星实时高清地图

- 极光加速器让你的网络速度飞起来

- 精美PPT制作模板推荐

- qq旧版本大全官方下载哪里可以找到?

- 手机版PS软件推荐(让你的手机照片秒变专业级作品)

- 破解版软件下载安全吗?

- 如何将糖豆广场舞下载安装到桌面

- 360抢票浏览器怎么使用?

- 为什么现在的女生越来越难脱单?解析背后的原因

- 智能ABC输入法教程轻松掌握打字技巧

- 灵府仙缘(一部神秘的修仙小说)

- 精美壁纸图片分享(让你的电脑桌面变得更美丽)

- 腾讯新闻app客户端下载(最新版本下载地址)

- 腾讯播放器(全面解析腾讯播放器的功能和使用方法)

- 如何在听中国有声小说官网上畅听经典(完整攻略分享)

- 炫舞官网是哪个?

- 抢救你的驾照交通违章查询官网大揭秘

- 04-0124PCIE 参考时钟架构

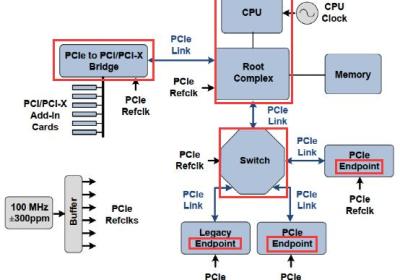

一、PCIe架构组件 首先先看下PCIE架构组件,下图中主要包括: ROOT COMPLEX (RC) (CPU); PCIE PCIPCI-X Bridge; PCIE SWITCH; PCIE ENDPOINT (EP) (p...

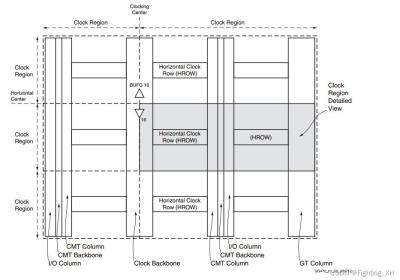

- 03-2024零基础学FPGA(六):FPGA时钟架构(Xilinx为例,完整解读)

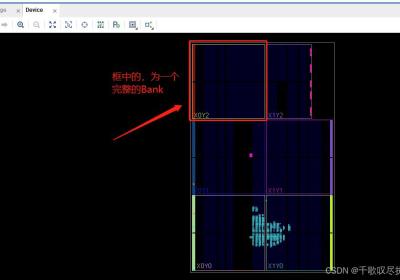

目录日常·唠嗑一、时钟资源(及布线)概述二、时钟架构-解读2.1、时钟整体架构2.2、时钟区域-内部架构2.2.1、区域整体2.2.2、区域细节三、时钟术语-解读(及使用方法)3.1、BUFG3.2、BUFH3.3、BUFIO...

- 02-2824【经验】STM32的一些细节

这两天 碰到的奇葩问题是 STM32定时器同步的问题。 我的设计本意是:使用定时器T3以100us的周期来定时发送命令给 FPGA。由于编码器出结果的最长时间为51us。因此,希望PWM中断要滞后于T3 约60us 。 调试过程:分别在T3...

- 02-1024如何利用在线时钟提高工作效率?

随着现代人们工作和生活节奏的加快,时间管理变得越来越重要。在这个时候,一个好的在线时钟工具可以帮助我们更好地管理时间,本文将介绍如何利用在线时钟1.选择适合自己的在线时钟在众多的在线时钟工具中,选择适合自己的是非常重要的。有些工具提供了更多...

- 02-0524【数字IC基础】跨时钟域(CDC,Clock Domain Crossing)

文章目录一、什么是跨时钟域?二、跨时钟域传输的问题?2、1 亚稳态(单bit:两级D触发器(双DFF))2、2 数据收敛(多bit亚稳态)(格雷码编码、握手协议、异步FIFO、DMUX)2、3 多路扇出:(先同步后扇出)2、4 数据丢失...

- 02-0424为什么时序逻辑电路会落后一拍?

1、时序逻辑电路落后一拍? FPGA初学者可能经常听到一句话:“时序逻辑电路,或者说用📣您有任何问题,都可以在评论区和我交流📃!📣本文由 孤独的单刀 原创,首发于C...

- 02-032451单片机LED点阵屏

LED点阵屏 LED点阵屏是一种由许多小型LED灯组成的矩阵式显示屏。这些LED灯可以是单色、双色或全彩的,它们排列成行和列的网格,可以根据需要点亮来显示图像、文字或动画等内容。LED点阵屏广泛应用于户外广告牌、室内显示、交通信号灯、电...

- 01-2524BUFGBUFGCEBUFHBUFHCEBUFHBUFGHCEBUFMRBUFMRCEBUFRIBU

本文对BUFGBUFGCEBUFHBUFHCE简单介绍,便于后续查看。原语的使用:在vivado中找到所要用的原语,直接将其实例化到设计中即可。 文章目录BUFGBUFGCEBUFHBUFHCEBUFMRBUFRBUFMRCE...

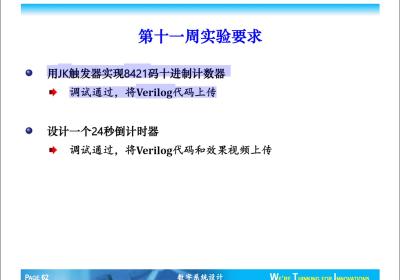

- 01-2524北邮22级信通院数电:Verilog-FPGA(11)第十一周实验(1)用JK触发器实现8421码十

北邮22信通一枚~ 跟随课程进度更新北邮信通院数字系统设计的笔记、代码和文章 持续关注作者 迎接数电实验学习~ 获取更多文章,请访问专栏: 北邮22级信通院数电实验_青山如墨雨如画的博客-CSDN博客目录一.代码部分 1.1 JK...

- 01-2524FPGA时序约束--实战篇(Vivado添加时序约束)

前面几篇文章已经详细介绍了FPGA时序约束基础知识以及常用的时序约束命令,相信大家已经基本掌握了时序约束的方法。 今天介绍一下,如何在Vivado中添加时序约束,Vivado添加约束的方法有3种:xdc文件、时序约束向导(Constrain...

- 01-2524FPGA时序分析与约束(0)——目录与传送门

一、简介 关于时序分析和约束的学习似乎是学习FPGA的一道分水岭,似乎只有理解了时序约束才能算是真正入门了FPGA,对于FPGA从业者或者未来想要从事FPGA开发的工程师来说,时序约束可以说是一道躲不过去的坎,所以这个系列我...

- 01-1924FPGA时序分析与约束(8)——时序引擎

一、概述 要想进行时序分析和约束,我们需要理解时序引擎究竟是如何进行时序分析的,包括时序引擎如何进行建立分析(setup),保持分析(hold),恢复时间分析(recovery)和移除时间分析(removal)。 二、时序引...

- 01-1924设计约束文件SDC

设计约束文件SDC,全称Synopsys design constraints 主要包括以下内容 Units(Time,capacitance,Resistance,Voltage,Current,Power)单位(时间,电容,电阻,电压,...

- 01-1924基于FPGA的数字秒表设计(完整工程)

目录 概述 设计功能 数字秒表设计的目的 模块仿真 设计代码 概述 该设计是用于体育比赛的数字秒表,基于FPGA在Quartus II 9.0sp2软件下应用VHDL语言编写程序,采用ALTRA公司CycloneII系列的EP2C8Q2...

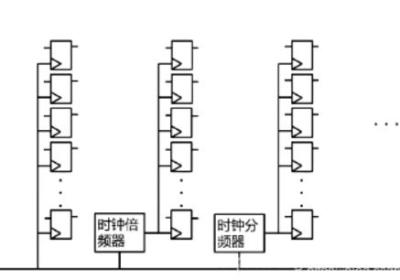

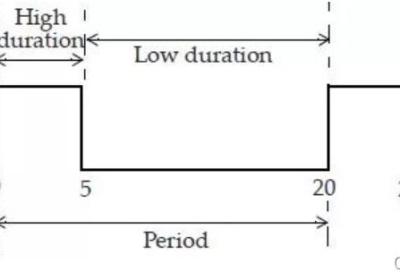

- 01-1924Verilog手撕代码(6)分频器

目录分频概念偶数分频二分频任意偶数占空比问题奇分频非常规占空比的奇分频分频时钟的使用小数分频分频概念 分频就是生成一个新时钟,该新时钟的频率是原有时钟频率的整数分之一倍,新周期是原有周期的整数倍。 再简单来说,让你手撕一个四...

- 01-1924【计算机架构】响应时间和吞吐量 | 相对性能 | 计算 CPU 时间 | 指令技术与 CPI | T

目录 0x00 响应时间和吞吐量(Response Time and Throughput) 0x01 相对性能(Relative Performance) 0x02 执行时间测量(Measuring Execution Time) 0x0...

- 08-2523做公司网站需要多少钱:线上时钟误差调整方法和注意事项

在这个高速运转的数字化时代,我们常常依赖于各种在线服务。在线时钟是其中一个最常用的服务之一。然而,你可能发现,你的电脑或手机上的在线时钟与你周围其他墙上时钟或手表有几秒钟的误差。这是因为在线时钟的运行并非精准无误,需要校准才能确保精确性。本...