- 23 | 负载均衡:选择Nginx还是OpenResty?

- re:Invent 构建未来:云计算&生成式 AI 诞生科技新

- 【论文笔记】Mamba:挑战Transformer地位的新架构

- mysql 事务详解一

- Node.js版本升级,修改模块默认的保存位置

- 【MySQL】内外连接——内连接、外连接、左外连接、右外连接、内外连接

- HashMap源码解读(中篇)

- 网络编程套接字(1)—网络编程基础

- AIGC元年大模型发展现状手册

- SQL中的CASE WHEN语句:从基础到高级应用指南

- SpringBoot中集成LiteFlow(轻量、快速、稳定可编排的组

- PHP教程:PHP如何利用post与get方式传值接收数据

- ELFK日志分析系统之搭建ELF+Filebeaat+Zookeepe

- Nginx:配置文件详解

- Golang和Java的对决:从设计理念到工具链的全面比较

- java.lang.NoClassDefFoundError: org

- 如何选择适合的 MySQL ConnectorJ 版本

- 5 万字 124 道MySQL经典面试题总结(2024修订版)

- 神州云服务平台(型号:DCC-CRL1000)基本配置教学视频

- Spring之BeanPostProcessor

- 【无线网络技术】——无线局域网(学习笔记)

- 【Jenkins PipeLine】Jenkins PipeLine

- Prometheus实战篇:Prometheus监控nginx

- 投springer的期刊时,遇到的一些latex模板使用问题

- 「SpringBrick快速入门指南」:一款基于Spring Boot

- com.google.common.collect 是 Google

- 宝塔面板安装Python和Flask(新版Python项目)

- Node.js 连接 mysql 数据库(Navicat)超详细!!!

- SpringCloudGateway之统一鉴权篇

- 【每日一题】LeetCode——链表的中间结点

本篇文章包含的内容

- 一、HDMI简介

- 1.1 HDMI引脚解析

- 1.2 HDMI工作原理

- 1.3 DVI编码

- 1.4 TMDS编码

- 二、并串转换、单端差分转换原语

- 2.1 原语简介

- 2.2 原语:IO端口组件

- 2.3 IOB 输入输出缓冲区

- 2.4 并转串原语`OSERDESE2`

- 2.4.1 `OSERDESE2` 工作原理

- 2.4.2 `OSERDESE2` 级联示意图

- 2.4.3 `OSERDESE2` 工作时序图

- 2.4.4 `OSERDESE2` 原语调用实例

- 2.5 单端转差分原语`OBUFDS`

笔者在这里使用的开发板是正点原子的达芬奇开发板,FPGA型号为XC7A35TFGG484-2。参考的课程是正点原子的课程手把手教你学达芬奇&达芬奇Pro之FPGA开发篇。

一、HDMI简介

HDMI,全称为High Definition Multimedia Interface,即高清多媒体接口。它不仅可以传输视频信号,还可以传输音频信号。上图所示的HDMI接口即为最常见的HDMI-A型接口。有19个引脚,尺寸为13.9×4.45mm,广泛应用于笔记本,投影仪,显示器等,工作频率约为160MHz。MDMI有不同的协议版本,比较重要的几个协议版本如1.0(2002.12)、1.3(2006.6)、2.0(2013.9)、2.1(2017.1),协议版本越高级,HDMI信号的传输速率、支持的分辨率以及帧率就越高。目前主流的HDMI协议版本为2.0。

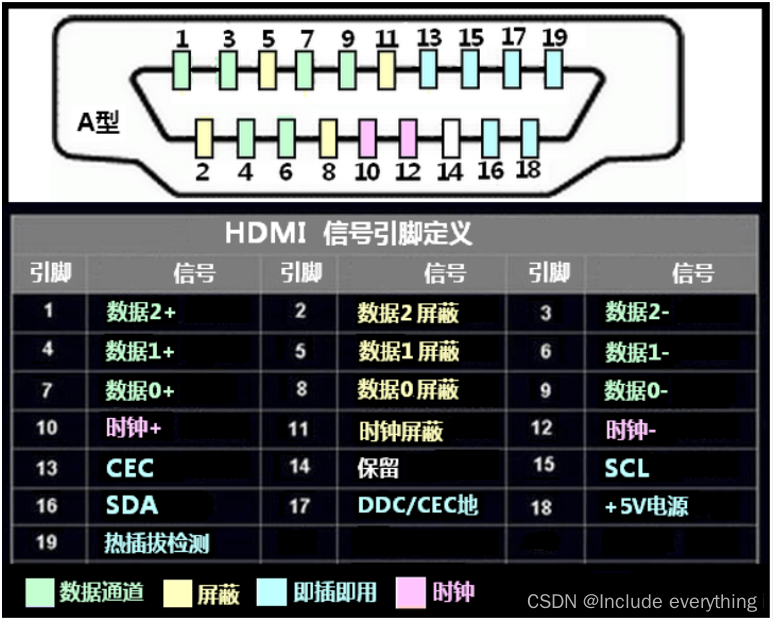

1.1 HDMI引脚解析

HDMI的引脚及其定义如下图所示:

在HDMI协议中,总共有4组差分线,每组分别由+信号、-信号、屏蔽信号组成。四组信号线分别传输R、G、B信号以及时钟信号。CEC为HDMI的扩展功能,可以使用这一条线传输两个设备之间的控制信息,SCL、SDA是HDMI的I2C接口,可以实现不同设备之间EDID信息传输(Extended Display Identification Data 、外部显示设备标识数据——指DDC通讯中传输的显示设备数据)。热插拔检测线用于检测是否有从机连接到主机。

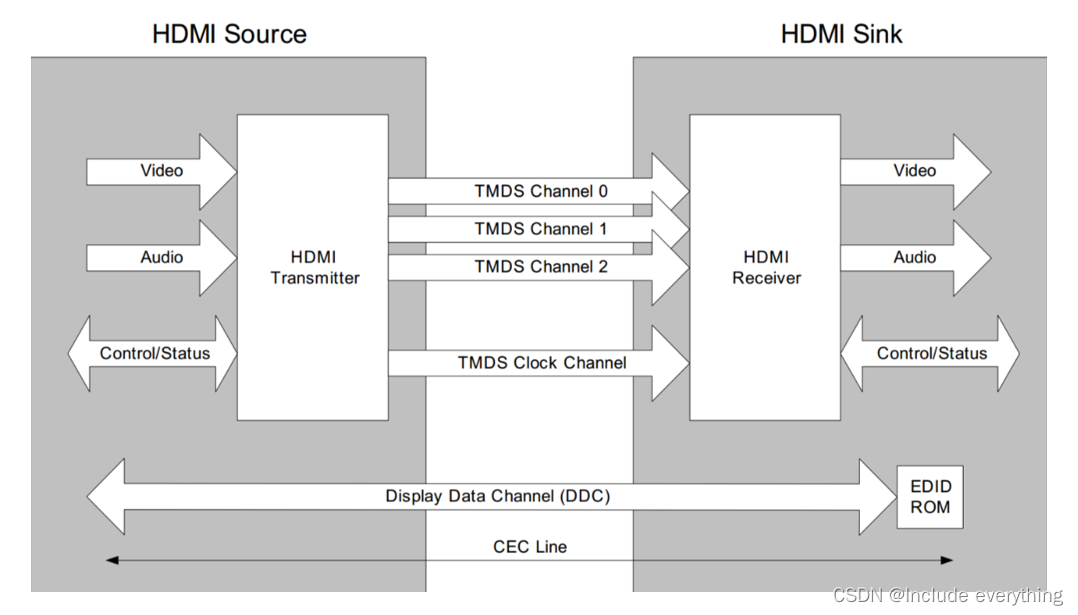

1.2 HDMI工作原理

HDMI的工作原理图如下所示。图中,TMDS指最小化传输差分信号(Transition Minimized Differential Signaling),是指被转换后的传输信号。视频信号Video和音频信号Audio通过一种特定的编码方式转换为10bit的串行差分信号,这种信号即成为TMDS信号。在主机上进行编码,在从机上进行解码,从而实现两个设备之间的信息交互。

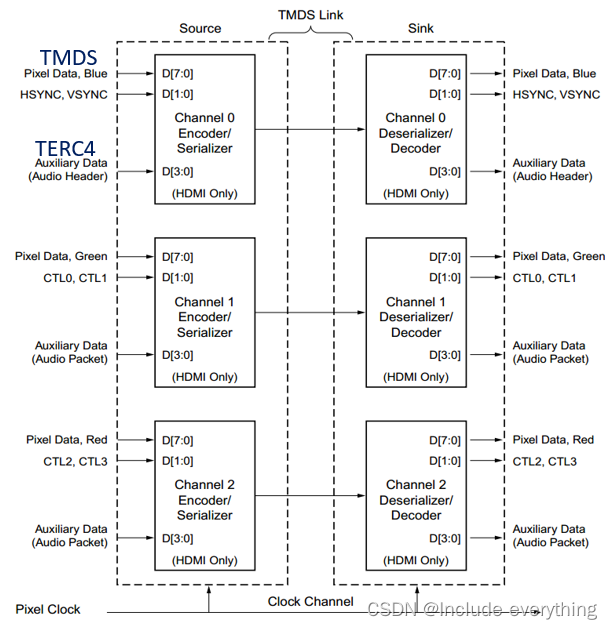

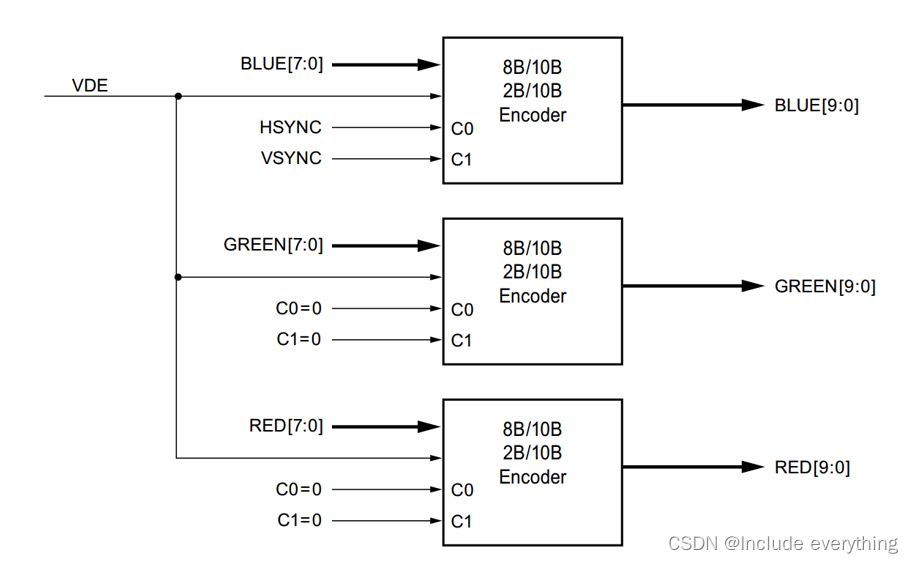

上图展示了RGB-888格式下的TMDS信号和TERC4转换以及连接方式。视频信息采用TMDS进行编码,音频信号采用TERC4进行编码。每一路信号都是并行信号,HSYNC和VSYNC是显示的水平同步信号和竖直同步信号,这两个信号只和蓝色通道一起编码。绿色通道和红色通道的CTL0-3用来传输控制信号。TERC4频编码较为复杂,本文章不涉及。时钟信号也需要编码,但是较为简单,上图中没有展示出来。

1.3 DVI编码

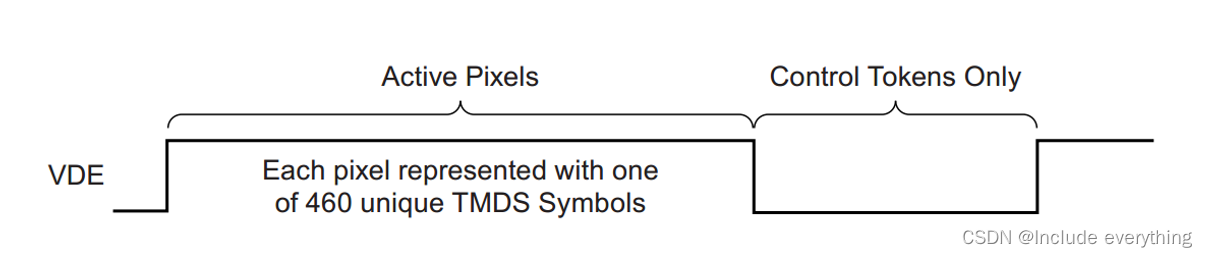

当HDMI只传递视频信息不传递音频信息,HDMI协议就可以退化为DVI协议。DVI也使用

TMDS进行编码。DVI编码中有一个视频数据使能VDE信号,当它拉高时传递像素信号,当它拉低时传递控制信号和水平数值同步信号。

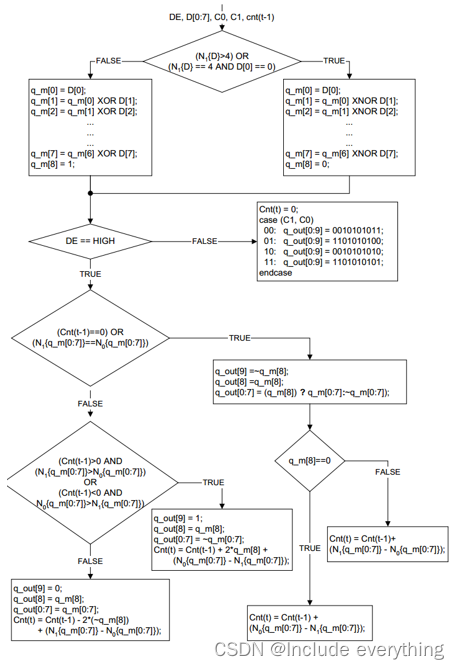

1.4 TMDS编码

TMDS指最小化传输差分信号(Transition Minimized Differential Signaling),主要适用于HDMI和DVI视频信号的编码。它的编码方式是将原有的8bit数据编码为10bit数据。

- 前8bit数据:通过同或/异或算法得到。

- bit9:反映前8bit数据的运算方式,如果是0,则说明前8bit通过异或非(同或)方式得到的,如果是1,就说明是通过异或方式得到的。

- bit10:直流平衡位。在高速的差分信号传输中,通常在接口处采用交流耦合,即会在接口处添加一个隔直电容去掉交流量。如果传输的信号长时间保持不变,就有可能在信号接收端出现直流偏移,导致解码错误。所以我们在编码时添加一个直流平衡位,如果前面数据1比较多,那么bit10 = 0,反之,如果前面数据0比较多,那么bit10 = 1。

TMDS的编码过程可以由下图所示:

参数名称 含义 D C1 C0 DE D是视频信号, C是控制信号, DE是使能信号 Cnt(t) 寄存器参数,用来存储第t次编码中1的个数比0的个数多多少(为了满足TMDS减少上冲下冲和确保直流平衡的要求) N1{x} 输入信号中1的个数 N0{x} 输入信号中0的个数 q_m 临时寄存的数据输出 q_out 编码输出 二、并串转换、单端差分转换原语

2.1 原语简介

原语:英文名称Primitive,是Xilinx针对其器件特征开发的一系列常用模块名称,涵盖了FPGA开发过程中的常用领域,方便用户直接调用FPGA的底层组件。以Xilinx为例,共分为10类:计算组件、IO端口组件、寄存器/锁存器、时钟组件、处理器组件、移位寄存器、配置和检测组件、RAM/ROM组件、Slice/CLB组件以及G-tranceiver。可以将原语理解为一段特殊的代码。实际上,调用原语是在实例化某个Xilinx的内置模块。

原语的好处在于原语可以之间看作为“库函数”,可以直接例化调用,比创建IP要更加方便,功能也更全面,可以有效提高开发效率。

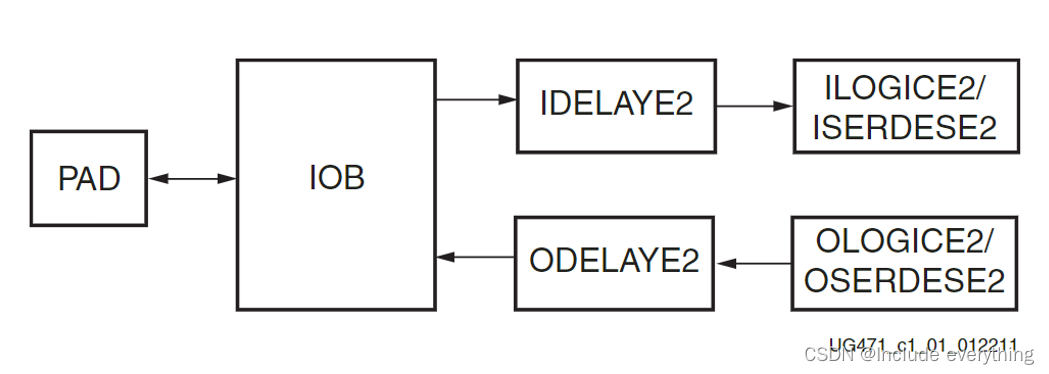

2.2 原语:IO端口组件

IO端口组件是Xilinx的一类原语。IO组件中一共包含了21个原语,对应21个功能。在本次实验中主要采用并转串OSERDES和单端转差分OBUFDS两个原语。

IO组件的结构如下图所示。图中IDELAYE2和ODELAYE2分别是输入延迟和输出延迟,主要作用是为了解决高速信号传输中信号线可能不等长的问题(等待最长的一根线数据到来后再读取数据)。ILOGICE2和OLOGICE2中主要包含了IDDR和ODDR的资源,用于双边沿取样。ISERDESE2的作用是将单端输入的串行数据转换为并行数据,OSERDESE2的作用是将并行数据转换为单端串行数据输出。

达芬奇使用的FPGA芯片为A7系列,其中没有HPBANK,所以没有ODELAYE2。ZYNQ也只有7030以上系列才有HPBANK,所以一般使用的FPGA芯片是没有ODELAYE2的。

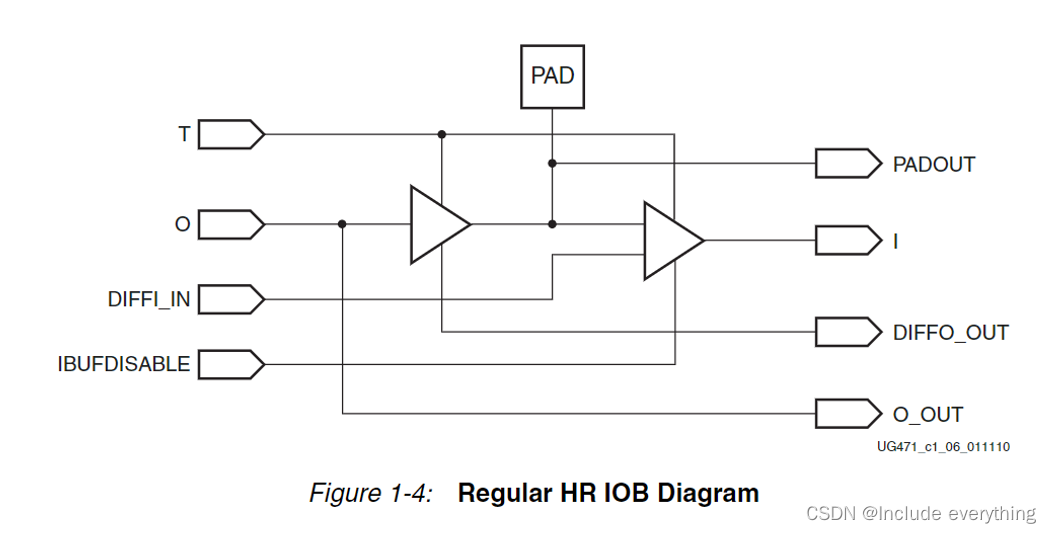

2.3 IOB 输入输出缓冲区

IOB的结构如下所示,在本次实验中它主要完成单端转差分的操作。因为差分信号至少需要两条线,所以一个IOB是无法完成的,至少需要两个IOB才能完成这个功能。

2.4 并转串原语OSERDESE2

2.4.1 OSERDESE2 工作原理

对于一个并行数据,要想把它转换为串行数据有以下两种做法:

- 一个时钟周期内有10bit数据,将该时钟作10倍频,倍频后的时钟每一个周期存放一个数据。这种做法易于理解,但是最大的问题是将时钟进行10倍频后芯片以及外部设备可能不支持这样高的频率。

- 一个时钟周期内有10bit数据,将该时钟作5倍频,倍频后的时钟的上升沿和下降沿都进行数据转换输出,即DDR双边沿采样。这样可以有效缓解倍频给时钟带来的压力。

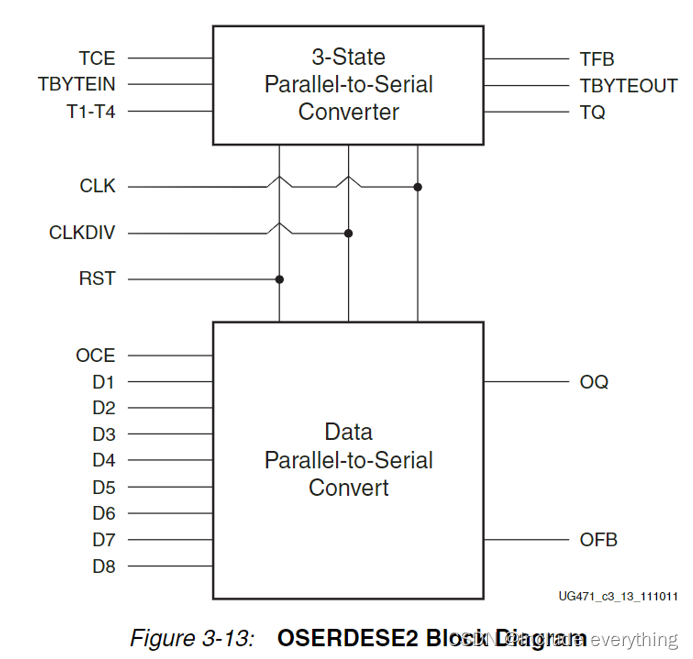

OSERDESE2的结构如下图所示。该组件可以分成三部分,上面的TCE,TBYTEIN和一部分电路组成三态控制;中间的CLK、CLKIDIV、RST组成时钟控制部分,CLK为快速时钟(5倍频),CLKDIV是低速时钟(1倍频);下面的OCE、D1-D8、OQ、OFB等组成并转穿的转换部分。数据转换数据只有8个数据输入口,要想实现10转1,则需要将两个OSERDESE2级联使用。

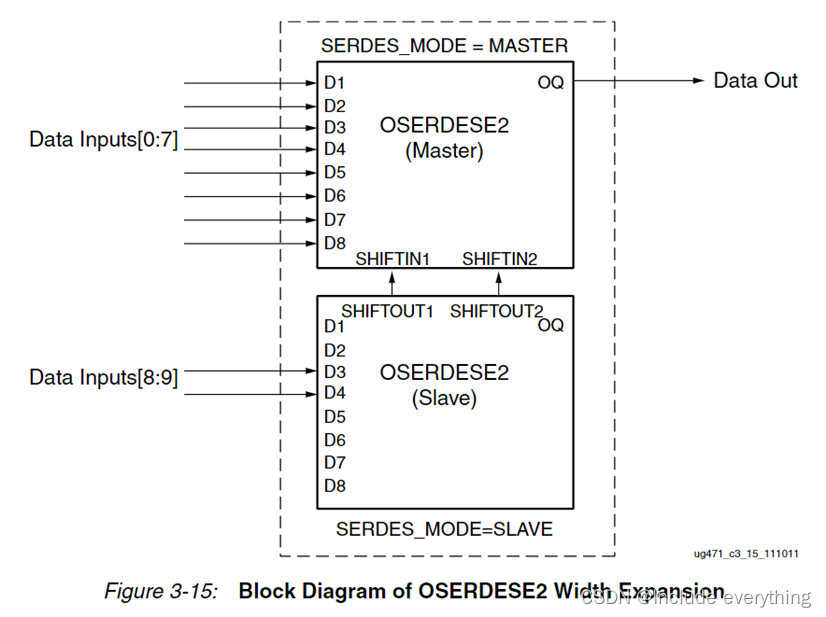

2.4.2 OSERDESE2 级联示意图

级联时需要注意:根据硬件的硬性要求,从模式的OSERDESE2的D1-D2不支持输入,只能从D3开始输入引脚,即可以选择D3-D8。

2.4.3 OSERDESE2 工作时序图

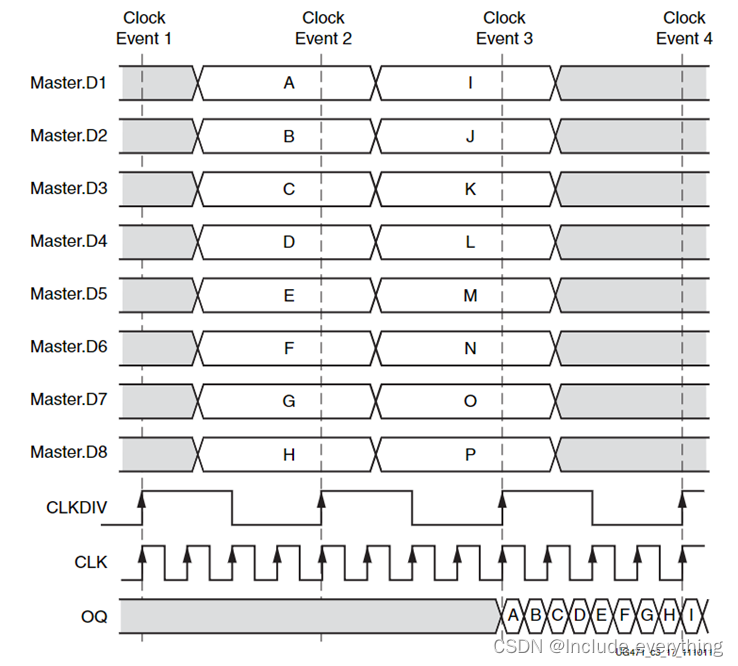

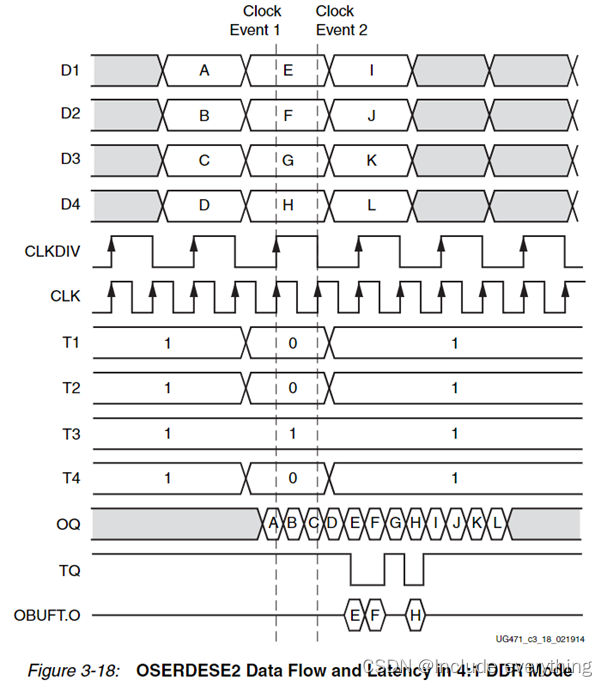

下面是OSERDESE2工作在普通模式和三态模式的两种时序工作图。第一张图数据为8位并行转串行,CLK和CLKDIV的周期之比为4:1。第二张图数据为4位并行转串行,并且包含T1-T4三态门控制,CLK和CLKDIV的周期之比为2:1。

T1-T4均为高电平有效,对应TQ将要输出的数据。且在当前CLKDIV周期采样,下个周期输出。在TQ高电平期间,可以执行输入操作。

2.4.4 OSERDESE2 原语调用实例

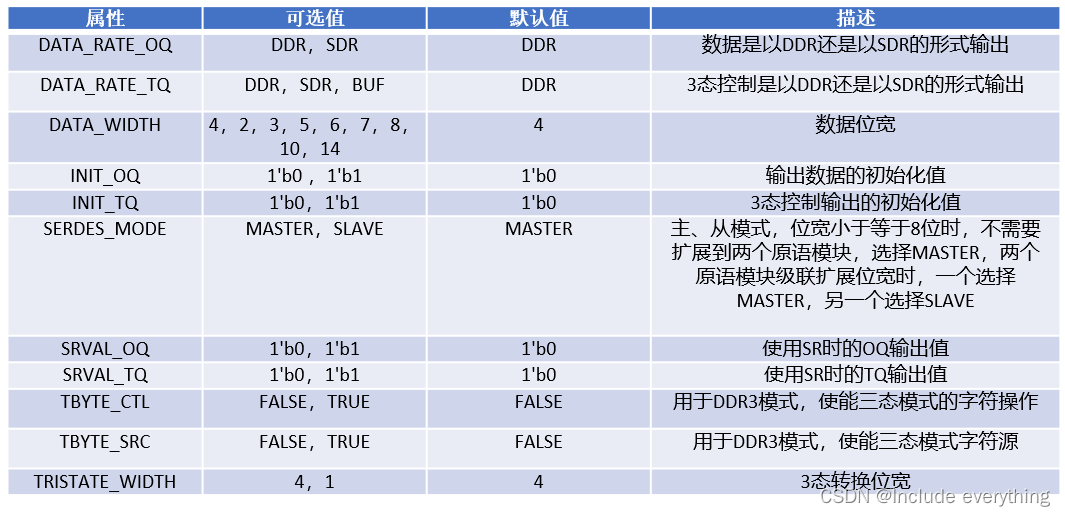

在原语调用实例中,需要特别注意以下几个参数:

- .DATA_RATE_OQ("DDR"):采用双边沿采样;

- .DATA_WIDTH(10):将要转换的数据宽度;

- .SERDES_MODE("MASTER"):设置级联下的主从模式;

- .SHIFTOUT1/2(SHIFTOUT1/2)、.SHIFTIN1/2(SHIFTIN1/2):级联下的数据线连接方式,注意不要连错。

OSERDESE2 #( .DATA_RATE_OQ("DDR"), // DDR, SDR .DATA_RATE_TQ("DDR"), // DDR, BUF, SDR .DATA_WIDTH(10), // Parallel data width (2-8,10,14) .INIT_OQ(1'b0), // Initial value of OQ output (1'b0,1'b1) .INIT_TQ(1'b0), // Initial value of TQ output (1'b0,1'b1) .SERDES_MODE("MASTER"), // MASTER, SLAVE .SRVAL_OQ(1'b0), // OQ output value when SR is used (1'b0,1'b1) .SRVAL_TQ(1'b0), // TQ output value when SR is used (1'b0,1'b1) .TBYTE_CTL("FALSE"), // Enable tristate byte operation (FALSE, TRUE) .TBYTE_SRC("FALSE"), // Tristate byte source (FALSE, TRUE) .TRISTATE_WIDTH(4) // 3-state converter width (1,4) ) OSERDESE2_inst ( .OFB(OFB), // 1-bit output: Feedback path for data .OQ(OQ), // 1-bit output: Data path output // SHIFTOUT1 / SHIFTOUT2: 1-bit (each) output: Data output expansion (1-bit each) .SHIFTOUT1(SHIFTOUT1), .SHIFTOUT2(SHIFTOUT2), .TBYTEOUT(TBYTEOUT), // 1-bit output: Byte group tristate .TFB(TFB), // 1-bit output: 3-state control .TQ(TQ), // 1-bit output: 3-state control .CLK(CLK), // 1-bit input: High speed clock .CLKDIV(CLKDIV), // 1-bit input: Divided clock // D1 - D8: 1-bit (each) input: Parallel data inputs (1-bit each) .D1(D1), .D2(D2), .D3(D3), .D4(D4), .D5(D5), .D6(D6), .D7(D7), .D8(D8), .OCE(OCE), // 1-bit input: Output data clock enable .RST(RST), // 1-bit input: Reset // SHIFTIN1 / SHIFTIN2: 1-bit (each) input: Data input expansion (1-bit each) .SHIFTIN1(SHIFTIN1), .SHIFTIN2(SHIFTIN2), // T1 - T4: 1-bit (each) input: Parallel 3-state inputs .T1(T1), .T2(T2), .T3(T3), .T4(T4), .TBYTEIN(TBYTEIN), // 1-bit input: Byte group tristate .TCE(TCE) // 1-bit input: 3-state clock enable );2.5 单端转差分原语OBUFDS

OBUFDS的调用较为简单,直接按照如下的格式调用即可。

OBUFDS OBUFDS_inst ( .O(O), // 1-bit output: Diff_p output (connect directly to top-level port) .OB(OB), // 1-bit output: Diff_n output (connect directly to top-level port) .I(I) // 1-bit input: Buffer input );

持续不定期更新完善中……

原创笔记,码字不易,欢迎点赞,收藏~ 如有谬误敬请在评论区不吝告知,感激不尽!博主将持续更新有关嵌入式开发、FPGA方面的学习笔记。