您的位置:上海毫米网络优化公司 > 网站优化分享 >

相关推荐recommended

- 【python】flask执行上下文context,请求上下文和应用上

- 22年国赛tomcat后续(653556547)群

- Windows 安装 Apache 和 PHP的详细步骤

- No ‘Access-Control-Allow-Origin‘ he

- 【手写数据库toadb】toadb表对象访问操作,存储管理抽象层软件架

- 在VBA中使用SQL

- com.google.common.collect 是 Google

- 金融支付系统中的云计算与边缘计算

- Llama2模型本地部署(Mac M1 16G)

- Java实战:Spring Boot集成Swagger3

- 【JavaEE】Spring Web-MVC

- 爬个数据这么吃力?别慌,代理IP轻松解决跨境电商技术瓶颈

- 【接口测试】常见HTTP面试题

- 升级php版本(简单明了,轻松升级php任意版本)

- mysql中varchar长度为多少

- 新零售门店、商品、会员管理指标体系总览

- 【python】深入探讨flask是如何预防CSRF攻击的

- 12.Mysql 多表数据横向合并和纵向合并

- Go学习(四):golang连接mysql数据库查询数据库信息

- 【vue2】近期bug收集与整理02

- IntelliJ IDEA 2023.3 的 AI Assistant

- SQLite、MySQL 和 PostgreSQL 数据库速度比较(本

- AI小说推文工具,一键生成AI视频推文助手

- MySQL 字段属性解读:理解无符号(UNSIGNED)数值类型的含义

- [运维] 可视化爬虫易采集-EasySpider(笔记)

- 企业级双活NGINX+图形化GUI管理搭建详细教程 nginx+kee

- 【CSDN活动】人工智能:前沿科技中的创业机遇与挑战

- Mybatis Plus 打印 SQL 语句(包含执行耗时)

- [架构之路-214]- UML-类图图解、详解、结构化、本质化讲解

- 基于chow算法的5G超密集网络功率分配matlab仿真

【上海大学数字逻辑实验报告】七、中规模元件及综合设计

作者:mmseoamin日期:2024-01-25

一、实验目的

- 掌握中规模时序元件的测试。

- 学会在Quartus II上设计序列发生器。

二、实验原理

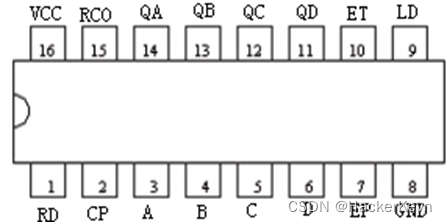

- 74LS161是四位可预置数二进制加计数器,采用16引脚双列直插式封装的中规模集成电路,其外形如下图所示:

其各引脚功能为:

异步复位输入端:RD 计数使能输入端:ET、EP

时钟输入端:CP 进位输出端:RCO

电源输入端:VCC 接地端:GND

预置端:LD 预置数据输入端:A、B、C、D

计数值输出端:QA、QB、QC、QD

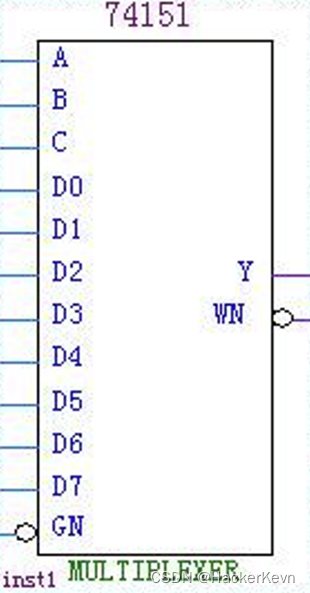

- 74LS151是8选1数据选择器,其外形如下图所示:

其各引脚功能为:

地址输入端:C、B、A(A为低位)

选择输入端:D0、D1、D2、D3、D4、D5、D6、D7

选通输入端:GN

互补输出端:Y、WN

三、实验内容

实验任务一:用74LS161芯片构造模10计数器

(1) 实验步骤

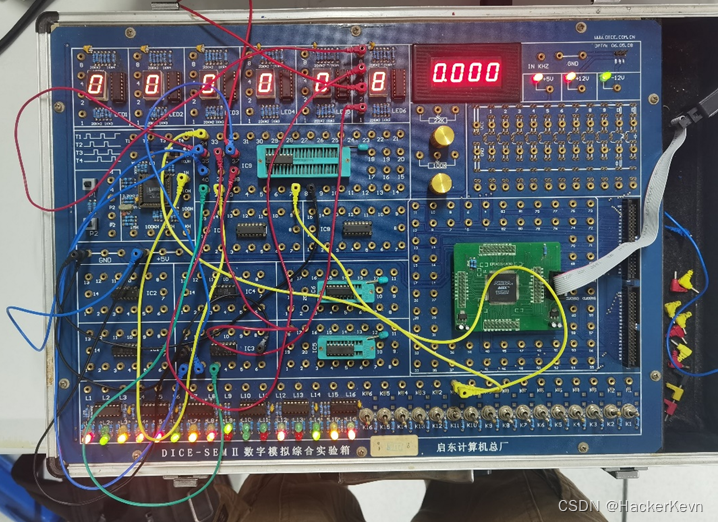

- 将74LS161的计数使能输入端EP和ET同时连接到K11,然后将计数值输出端QA、QB、QC、QD分别连接到数码管LED6的1、2、4、8接口,同时将QB和QD分别连接到74LS00的输入引脚1A和1B,输出引脚连接回74LS161的异步复位输入端RD,最后将时钟输入端CP连接到连续脉冲1H并将74LS161和74LS00接电接地后构成模10计数器,如下图所示:

- 拨动开关,观察数码管的变化。

(2) 实验现象

开始时,计数器的值为0,而后每次时钟脉冲到达时,计数器的值依次增加,当计数器的值达到最大值也就是9时,它将从0重新开始计数。

(3) 实验结论

通过74LS161作为搭建平台,我们成功地实现了一个模10计数器。实验结果表明,计数器能按照预期进行模10计数。

实验任务二:在Quartus II设计一个二进制序列01100111发生器

(1) 实验步骤

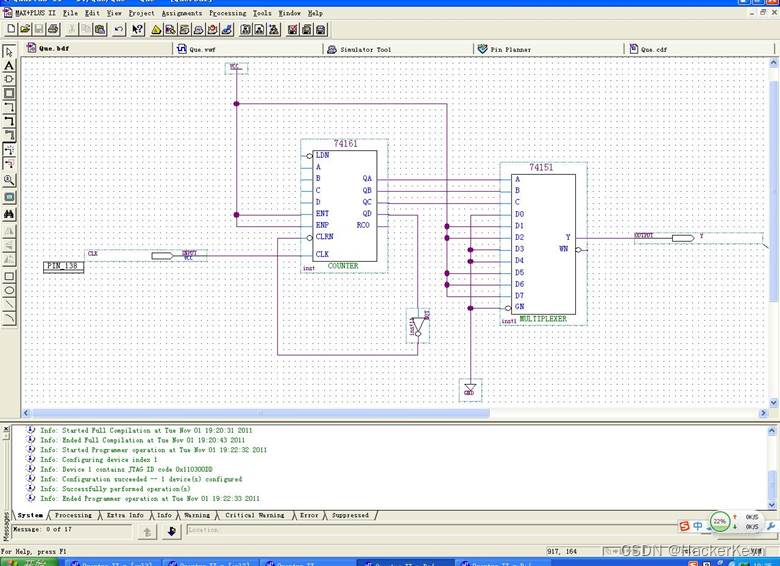

- 用Quartus II设计出如下电路:

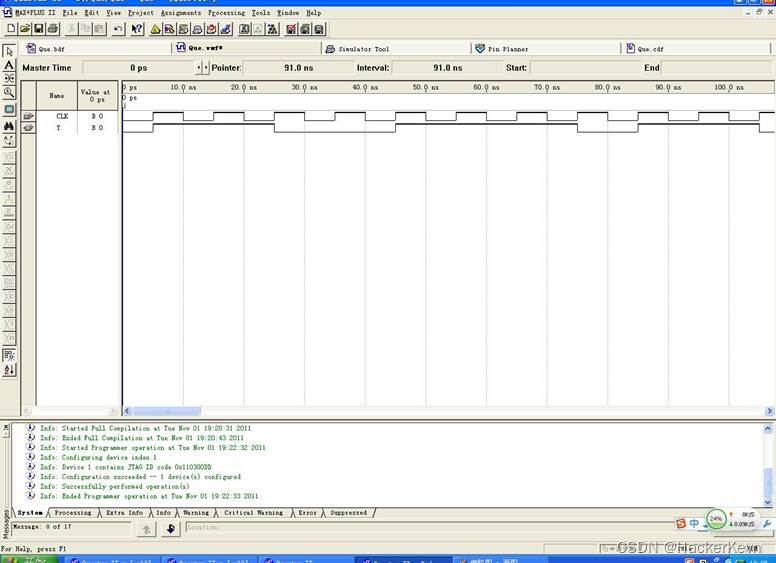

- 编译通过后进行波形仿真,验证电路逻辑功能:

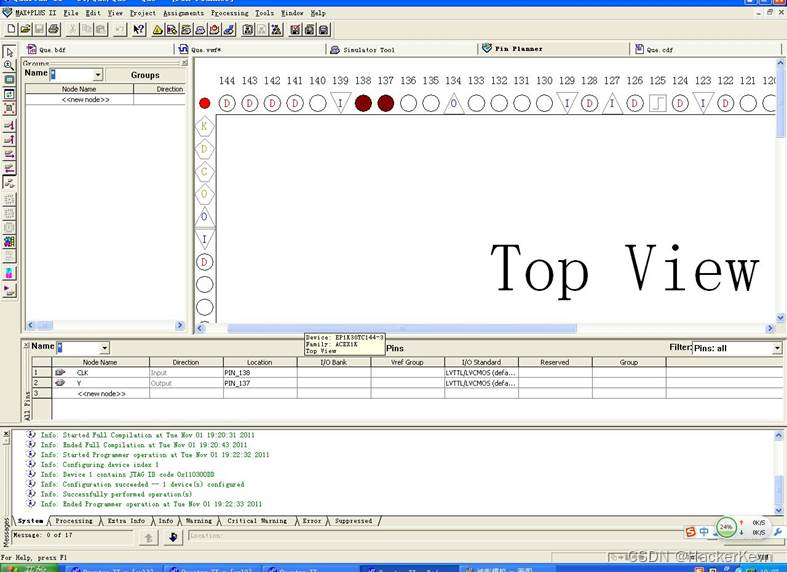

- 仿真通过后,参照原理图定义引脚:

- 生成编程并将文件下载到FPGA。

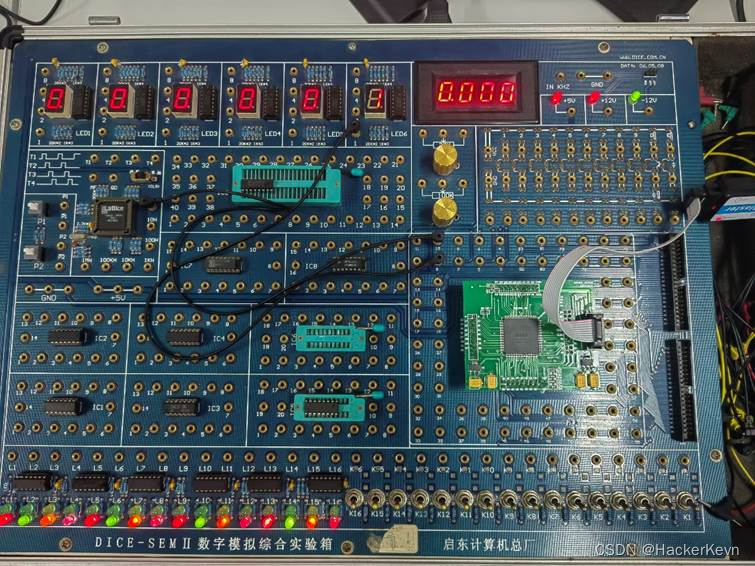

- 将开关连接对应的输入引脚,输出引脚连接到发光二极管:

- 用开关和发光二极管测试FPGA的功能。

- 记录测试结果。

(2) 实验现象

电路运行时,随着时钟脉冲的到达,LED灯按照01100111的序列进行变化,符合预期行为。

(3) 实验结论

通过使用Quartus II设计工具,我们成功地用74LS161和74LS151设计了一个二进制序列01100111发生器。实验结果表明,数据会按照时钟脉冲的触发依次产生序列中的数,符合预期行为。

四、建议和体会

- 在实验前,要熟悉74LS161和74LS151的原理。

- 实现序列发生器时,要注意观察LED灯的变化,以确保实验结果的准确性。

- 本实验有助于增进对模10计数器和序列发生器的理解,同时帮助我们初步掌握了中规模元件的设计方法,为后续进行更复杂的电路设计打下基础。