您的位置:上海毫米网络优化公司 > 网站优化分享 >

相关推荐recommended

- MongoDB【四】查询与聚合框架

- Mysql 将数据按照年月分组 统计

- Devin内测注册全攻略:一文带你快速体验最新AI软件工程师技术 ️

- 实战演练 | 使用 Navicat 进行 MySQL 数据同步

- Java八股文(Spring Boot)

- 开源浏览器Firefox:使用Docker本地部署并远程访问进行测试

- GOPROXY 代理设置

- Spring Boot框架的过滤器(Filters)和拦截器(Inte

- ELFK日志分析系统之搭建ELF+Filebeaat+Zookeepe

- 解决,“该设备或资源(Web 代理)未设置为接受端口“7890”上的连

- ping命令使用示例解析

- 【Linux系列】Linux判断架构信息

- 代码插入数据库数据时报错:Cause: com.mysql.cj.jd

- Spring Cloud - 手写 Gateway 源码,实现自定义局

- ruoyi-vue(若依前后端分离版本)环境搭建 用idea 安装re

- SpringBoot 解决跨域问题的 5 种方案!

- Rustdesk开源远程连接-自搭建服务器

- Mybatis之批量更新数据

- uniapp:uview-plus的一些记录

- 图论(算法竞赛、蓝桥杯)--Dijkstra算法最短路

- 2-1.Hadoop大数据集群搭建之---本地模式

- 网络编程套接字(1)—网络编程基础

- 新一代开源数据可视化平台 datart——技术架构与应用场景

- SpringBoot整合Minio的详细步骤

- Django学习(1):Django项目的初步创建与简单配置

- 【排序】排序这样写才对Ⅰ --插入排序与选择排序

- Kafka(Windows)安装配置启动(常见错误扫雷)教程

- 从零开始实现C++ TinyWebServer(九)---- 项目知识

- 【算法专题】FloodFill 算法

- MySQL中replace into详解、批量更新、不存在插入存在则更

数码管移位循环显示数字verilog代码ego1开发板

作者:mmseoamin日期:2024-02-04

名称:数码管移位循环显示数字verilog代码ego1开发板

软件:VIVADO

语言:Verilog

代码功能:

采用EGO1中的两组数码管,让该8个数码管循环显示:01234567,12345678,23456789....

电路的输入信号en进行启动或暂停;用按键控制循环,按一下显示下一组数。

FPGA代码Verilog/VHDL代码资源下载:www.hdlcode.com

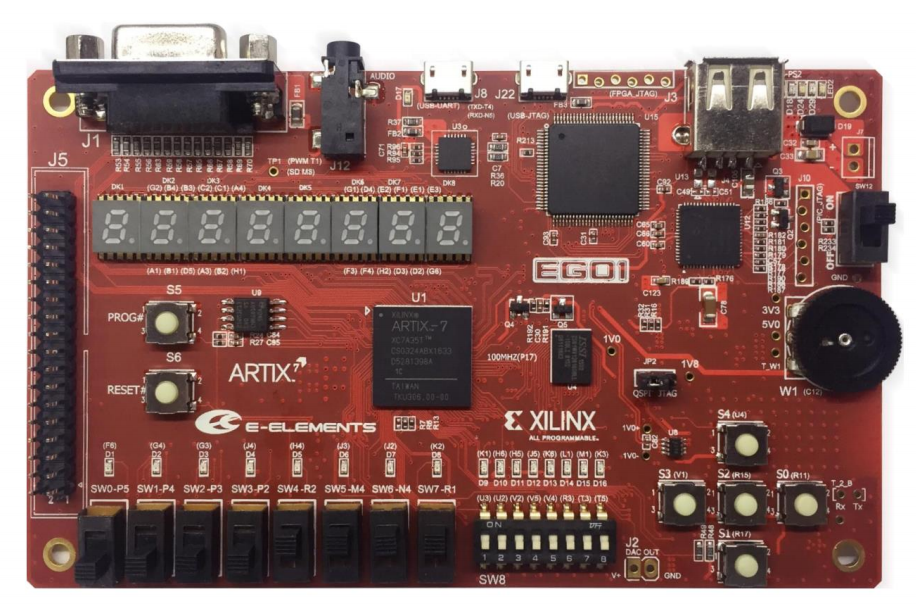

本代码已在ego1开发板验证,开发板如下,其他开发板可以修改管脚适配:

代码下载:数码管移位循环显示数字verilog代码ego1开发板名称:数码管移位循环显示数字verilog代码ego1开发板(代码在文末下载)软件:VIVADO语言:Verilog代码功能:采用EGO1中的两组数码管,让该8个数码管循环显示:01234567,12345678,23456789....电路的输入信号en进行启动或暂停;用按键控制循环,按一下显示下一组数。FPGA代码Verilog/VHDL代码资源下载:www.hdlcode.com本代码已在e http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=312

http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=312

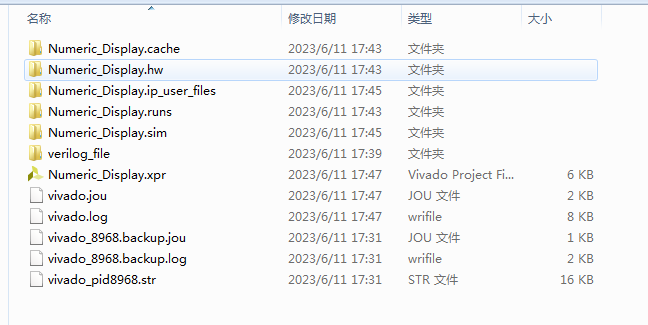

1. 工程文件

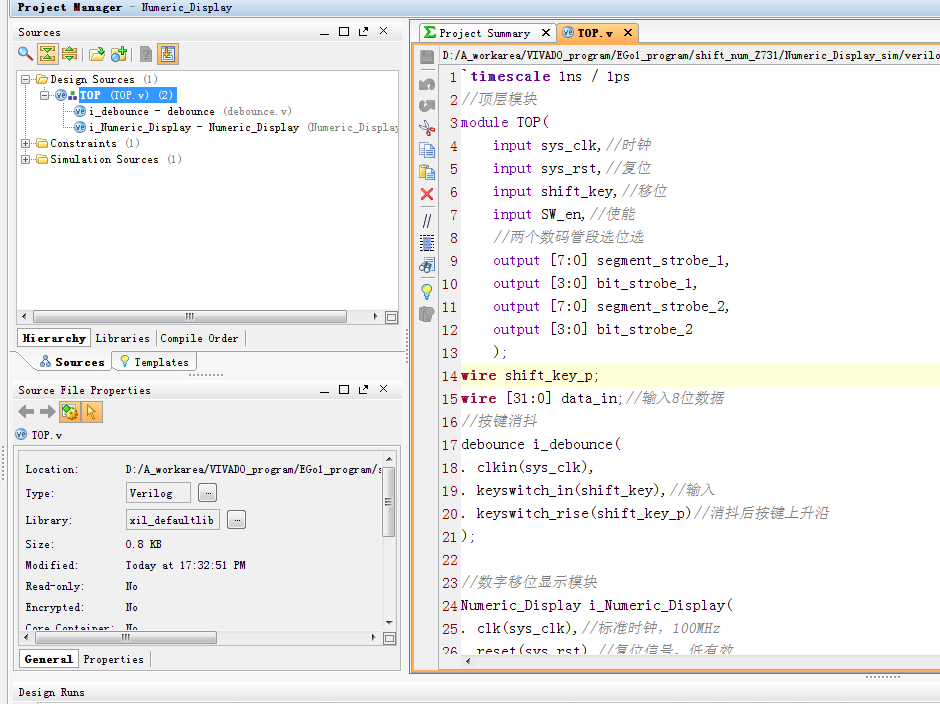

2. 程序文件

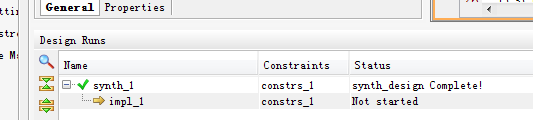

3. 程序编译

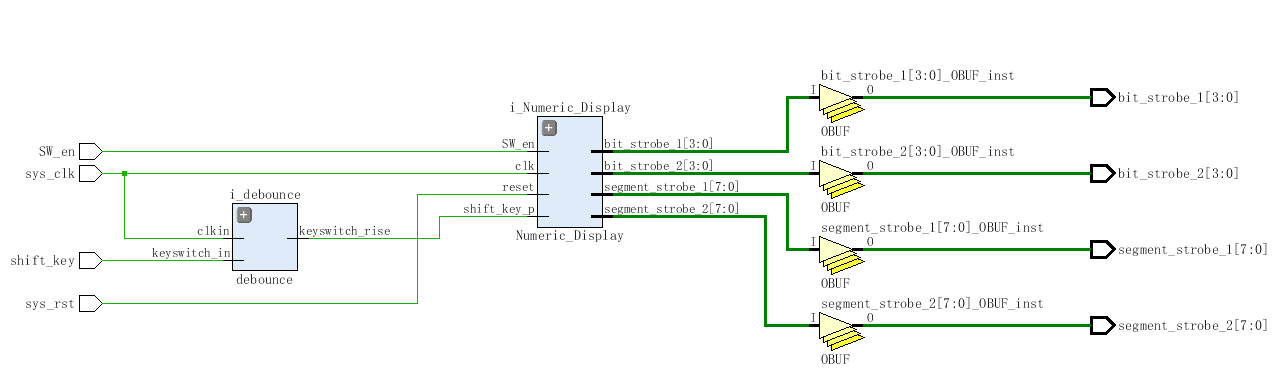

4. RTL图

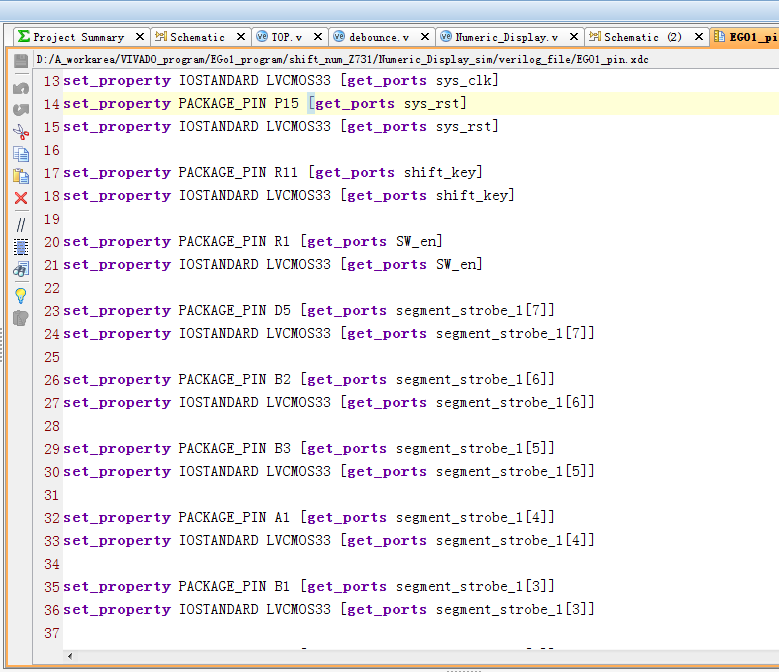

5. 管脚分配

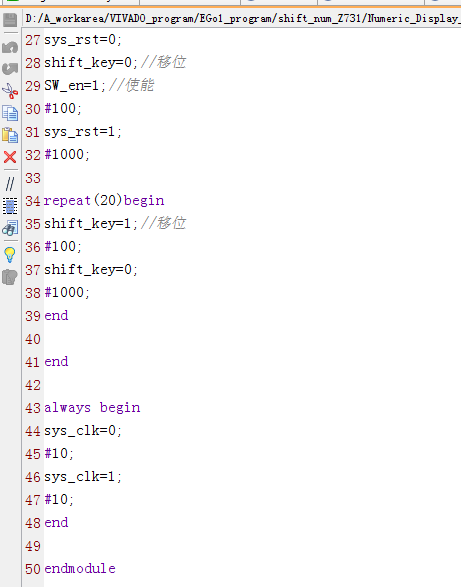

6. Testbench

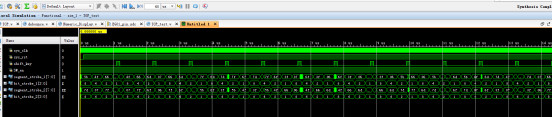

7. 仿真图

整体仿真图

按键消抖模块

显示模块

部分代码展示:

module Numeric_Display(

input clk,//标准时钟,100MHz

input reset,//复位信号,低有效

input SW_en,//使能

input shift_key_p,//移位

output reg [7:0] segment_strobe_1,

output reg [3:0] bit_strobe_1, //高电平点亮,高电平选通

output reg [7:0] segment_strobe_2,

output reg [3:0] bit_strobe_2//高电平点亮,高电平选通

);

reg [39:0] data_in;//输入8位数据

always @(posedge clk or negedge reset)

if(reset==0)

data_in<=40'h0123456789;

else if(SW_en==1)begin//使能

if (shift_key_p)//按下移位

data_in<={data_in[35:0],data_in[39:36]};//移位

end

reg [15:0] counter=16'd0;

always @(posedge clk)

begin

if (counter == 16'hffff)

counter <= 16'h0000;

else

counter <= counter + 1;//计数

end

reg [3:0] display_data_1;

reg [3:0] display_data_2;

//数码管1位选控制

always @(posedge clk)

case (counter[15:14])

2'd0 : begin

display_data_1 <= data_in[31:28];

bit_strobe_1 <=4'b1000;

end

2'd1 :begin

display_data_1 <= data_in[27:24];

bit_strobe_1 <=4'b0100;

end

2'd2 :begin

display_data_1 <= data_in[23:20];

bit_strobe_1 <=4'b0010;

end

2'd3 :begin

display_data_1 <= data_in[19:16];

bit_strobe_1 <=4'b0001;

end

endcase

上一篇:IEPE与数据采集