您的位置:上海毫米网络优化公司 > 网站优化分享 >

相关推荐recommended

- 图论(算法竞赛、蓝桥杯)--Dijkstra算法最短路

- 【zlm】问题记录:chrome更新引起的拉不出webrtc; 证书校

- Jenkins 命令无法后台运行,使用BUILD

- 基于pear-admin-flask 的 flask 使用教程

- python——Django 框架

- SQL-窗口函数

- 惊艳的KMP字符串匹配算法

- 志愿服务管理小程序设计与实现 毕业设计-附源码97923

- 数据结构中的时间复杂度和空间复杂度基础

- PostgreSQL的date

- 虚幻引擎架构自动化及蓝图编辑器高级开发进修班

- Python贵州贵阳二手房源爬虫数据可视化分析大屏全屏系统

- Matlab方程组拟合【案例源码+视频教程】

- 【精·超简单】SpringBoot 配置多个数据源(连接多个数据库)

- 多模态之ALBEF—先对齐后融合,利用动量蒸馏学习视觉语言模型表征,学

- 解锁AI大模型潜力,让文案创作飞跃升级

- Linux升级nginx版本

- 大数据实验 实验四:NoSQL 和关系数据库的操作比较

- IDEA搭建spring boot时报错Error: Request

- 【MySQL】MySQL数据库主键自增长删除后ID不连续的问题及其解决

- Java实战:SpringBoot 业务操作日志功能设计

- 宝塔面板安装Python和Flask(新版Python项目)

- docker exec

- OpenHarmony开发-系统烧录

- vue-create 创建 VUE3项目-创建

- 详解实现黑马旅游网的ES和Mysql数据同步

- AI小说推文工具,一键生成AI视频推文助手

- 【Spring Cloud 进阶】OpenFeign 底层原理解析

- 在Flask中使用MySQL数据库

- 揭秘智慧礼品背后的故事

vivado 乘加器与累加器的ip仿真

作者:mmseoamin日期:2024-02-05

在使用乘法器和乘加器中遇到了一些问题,解决后仍有疑问,以此记录

乘法器

乘法器是指只有数据中只有乘法运算,运算时p=a*b

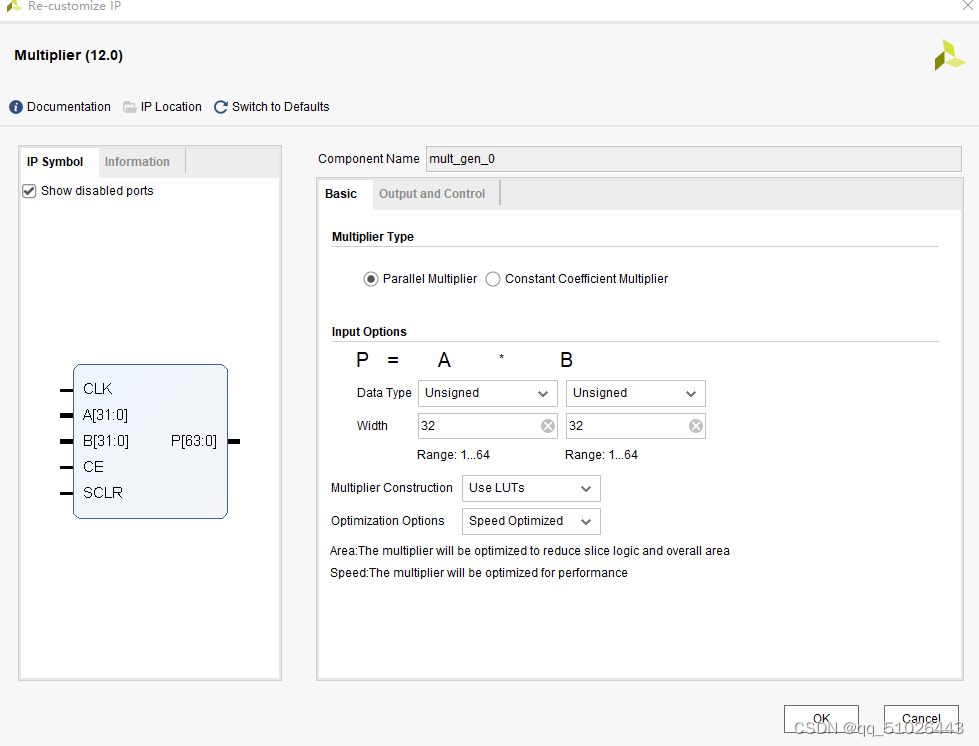

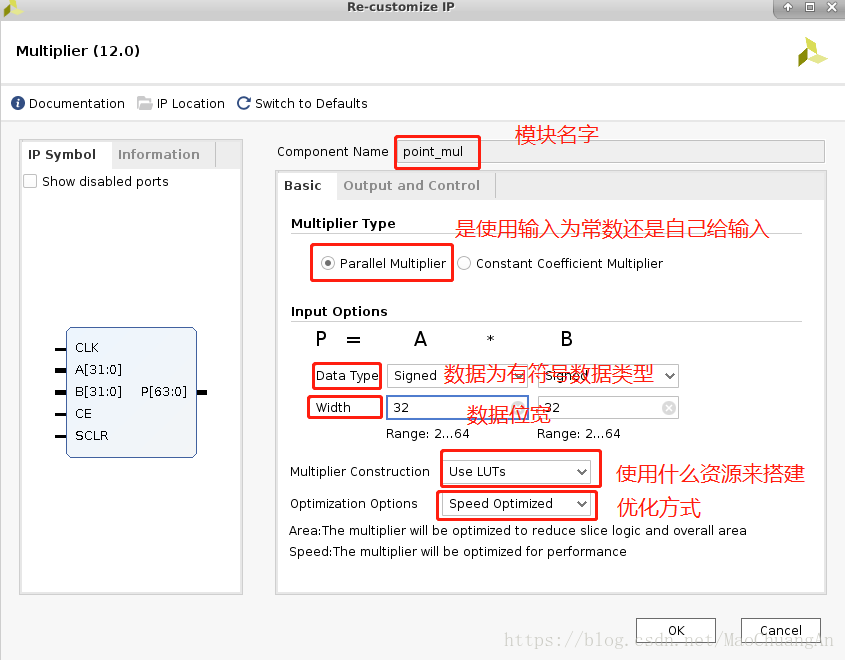

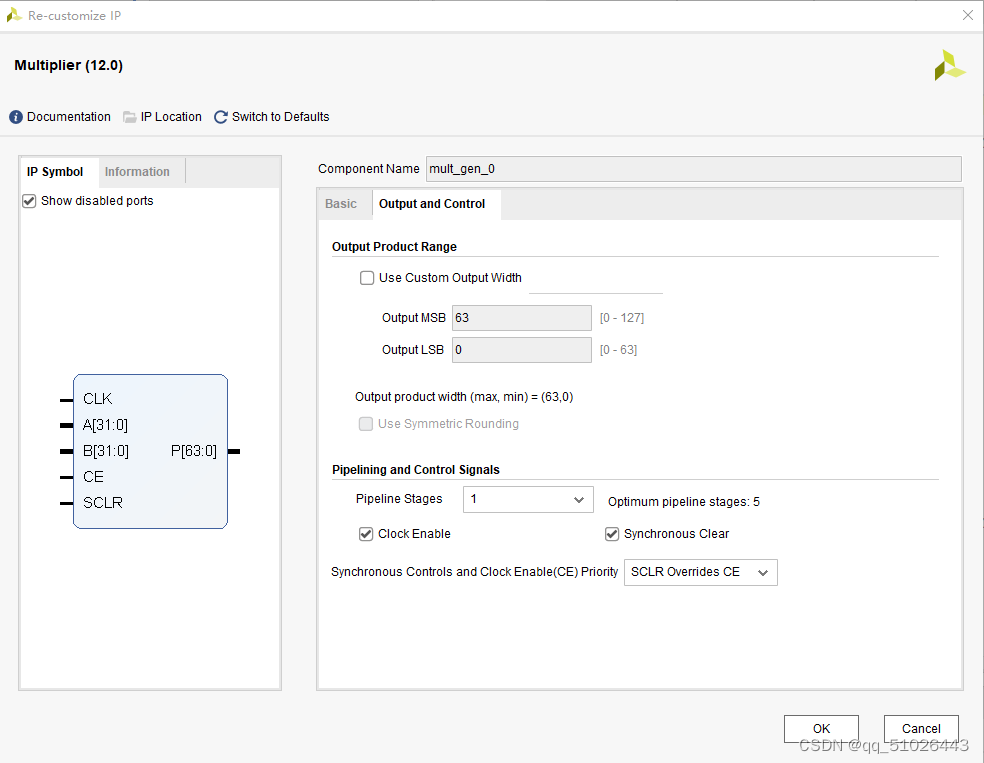

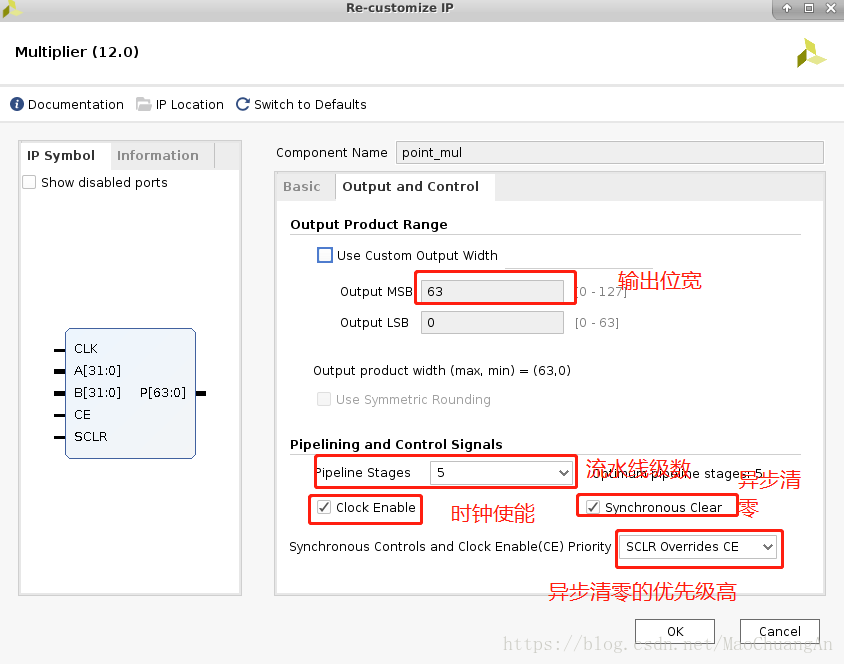

进行如下图所示设置

借用一张描

仿真代码

always #5 clk=~clk;

initial

begin

clk = 1;

a = 0;

b = 0;

ce = 0;

sclr = 1;

#100;

sclr = 0;

ce = 1;

a = 10;

b = 10;

#100;

ce = 0;

end

mult_gen_0 uut (

.CLK(clk), // input wire CLK

.A(a), // input wire [15 : 0] A

.B(b), // input wire [15 : 0] B

.CE(ce), // input wire CE

.SCLR(sclr), // input wire SCLR

.P(s) // output wire [31 : 0] P

);

endmodule

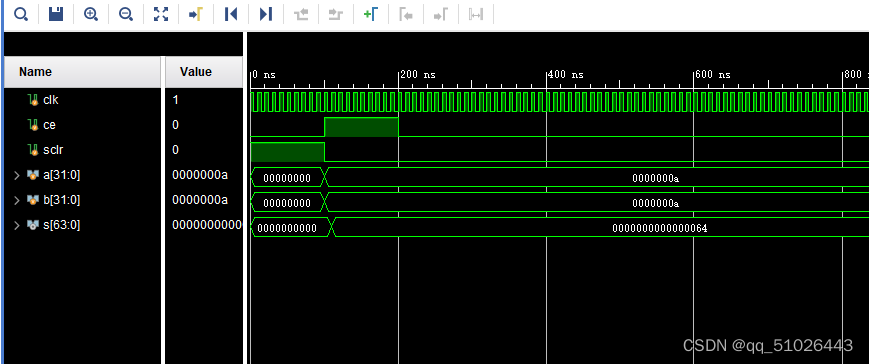

成功得到仿真结果100

乘加器

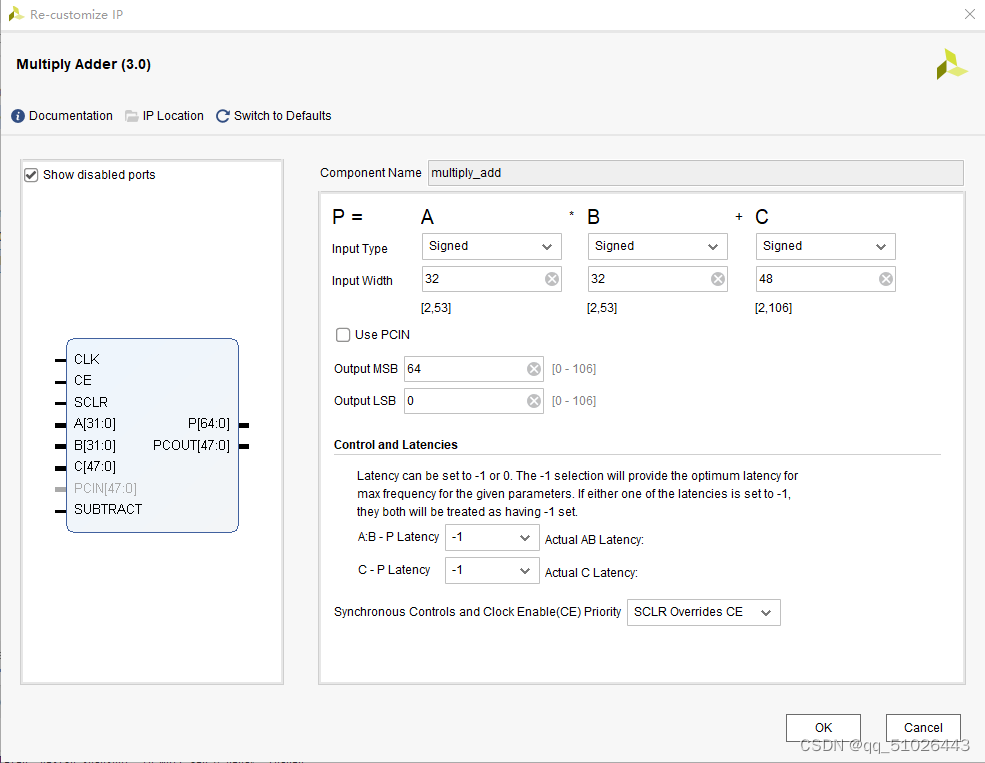

乘加器的运算时p=a*b+c,在此不进行+c的运算,只运行a*b的运算,并不进行级联运算

以下为端口定义

A[N:0] Input A输入(乘法操作数1)

B[M:0] Input B输入(乘法操作数2)

C[L:0] Input C输入(加减操作数)

PCIN Input 级联输入

SUBTRACT Input 控制加/减操作(1=减法,0=加法)

CE Input 时钟使能 (高有效)

CLK Input 时钟信号,上升沿有效

SCLR Input 同步复位,高有效

PCOUT Output 输出级联

P[Q:0] Output 输出端口

原文链接:https://blog.csdn.net/weixin_41445387/article/details/119777736

仿真代码

module tb_mult_gen_0;

// Inputs

reg clk;

reg ce;

reg sclr;

reg [31:0] a;

reg [31:0] b;

// Outputs

wire [63:0] s;

// Instantiate the Unit Under Test (UUT)

always #5 clk=~clk;

initial

begin

clk = 1;

a = 0;

b = 0;

ce = 0;

sclr = 1;

#100;

sclr = 0;

ce = 1;

a = 10;

b = 10;

#100;

ce = 0;

end

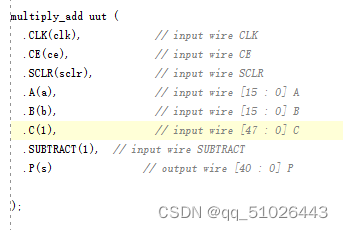

multiply_add uut (

.CLK(clk), // input wire CLK

.CE(ce), // input wire CE

.SCLR(sclr), // input wire SCLR

.A(a), // input wire [15 : 0] A

.B(b), // input wire [15 : 0] B

.C(0), // input wire [47 : 0] C

.SUBTRACT(0), // input wire SUBTRACT

.P(s) // output wire [40 : 0] P

);

endmodule

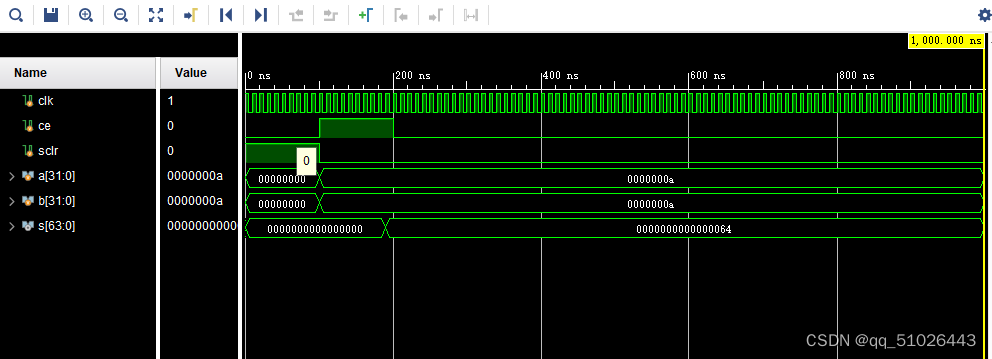

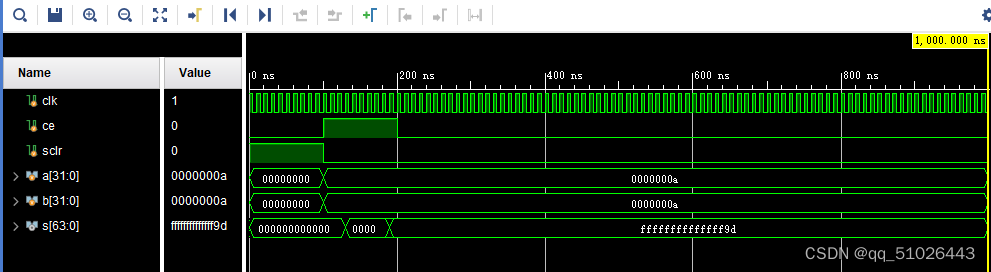

得到正确仿真结果100

但当

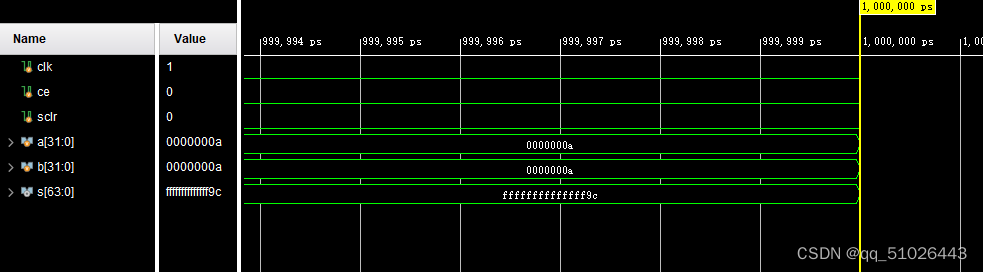

SUBTRACT(0)改为 SUBTRACT(1)时

输出结果为-100

将例化中c改为1

得到结果为-99

总结

所以乘加器在此次仿真时SUBTRACT 端口为0,乘出的结果为负,为1乘出的结果为正,再去加上c